¿Por qué utilizar Xilinx FPGA XC3S500E-4FTG256I?

Si eres diseñador de ingeniería electrónica, quizás conozcas el chip XC3S500E-4FTG256I .

Este conjunto de puertas programables en campo (FPGA) se usa ampliamente en diversas aplicaciones, desde electrónica de consumo hasta control industrial, aviación, militar y otros campos.

Un FPGA es un dispositivo semiconductor que consta de una matriz de bloques lógicos configurables (CLB) conectados a través de interconexiones programables. El usuario determina estas interconexiones programando SRAM. Un CLB puede ser simple (puertas AND, OR, etc.) o complejo (un bloque de RAM). La FPGA permite realizar cambios en un diseño incluso después de que el dispositivo esté soldado a una PCB.

En este artículo, aprenderá algunos conceptos básicos del XC3S500E-4FTG256I de Xilinx y también explorará la forma profesional de usarlo y sus funciones.

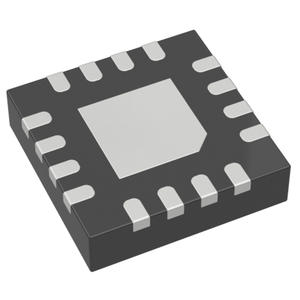

¿Qué es XC3S500E-4FTG256I?

XC3S500E-4FTG256I pertenece a la serie FPGA Spartan-3E, diseñada por Xilinx.

La familia Spartan-3E ofrece una solución FPGA rentable con bajo consumo de energía , alto rendimiento y funciones avanzadas a nivel de sistema.

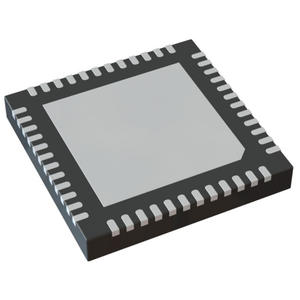

Xilinx Zynq FPGA

XC3S500E-4FTG256I cuenta con 500.000 puertas de sistema, 772 E/S de usuario y 36 RAM de bloque.

Funciona a una frecuencia máxima de 400MHz y tiene un rango de voltaje central de 1,14V a 1,26V.

XC3S500E-4FTG256I se utiliza comúnmente en aplicaciones como aeroespacial y de defensa, automoción, radiodifusión, consumo, informática de alto rendimiento, industrial, médica y científica, pruebas y mediciones.

Solicite Xilinx XC3S500E-4FTG256I FGPA original y nuevo ahora

Características de XC3S500E-4FTG256I

• Señalización SelectIO

- Hasta 633 pines de E/S

- Dieciocho estándares de señal de un solo extremo

- Ocho estándares de señal diferencial, incluidos LVDS y RSDS

- Compatibilidad con doble velocidad de datos (DDR)

• Recursos lógicos

- Abundantes celdas lógicas con capacidad de registro de desplazamiento

- Multiplexores anchos

- Lógica de acarreo de anticipación rápida

- Multiplicadores de 18 x 18 dedicados

- Lógica JTAG compatible con IEEE 1149.1/1532

• Seleccionar memoria jerárquica RAM

- Hasta 1728 Kbits de RAM de bloque total

- Hasta 432 Kbits de RAM distribuida total

• Administrador de reloj digital (cuatro DCM)

- Eliminación de desviación horaria

- Síntesis de frecuencia

- Desplazamiento de fase de alta resolución

English

English Español

Español Português

Português русский

русский français

français 日本語

日本語 Deutsch

Deutsch Tiếng Việt

Tiếng Việt Italiano

Italiano Nederlands

Nederlands ไทย

ไทย Polski

Polski 한국어

한국어 Svenska

Svenska magyar

magyar Malay

Malay বাংলা

বাংলা Dansk

Dansk Suomi

Suomi हिन्दी

हिन्दी Pilipino

Pilipino Türk

Türk Gaeilge

Gaeilge عربى

عربى Indonesia

Indonesia norsk

norsk čeština

čeština Ελληνικά

Ελληνικά Українська

Українська Javanese

Javanese فارسی

فارسی български

български ລາວ

ລາວ Latine

Latine Қазақ

Қазақ Euskal

Euskal Azərbaycan

Azərbaycan slovenský

slovenský Македонски

Македонски Lietuvos

Lietuvos Eesti Keel

Eesti Keel Română

Română Slovenski

Slovenski Српски

Српски 简体中文

简体中文 繁体中文

繁体中文 Беларус

Беларус